International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

#### SITES

Smart And Innovative Technologies In Engineering And Sciences

Gyan Ganga College of Technology Vol. 4, Special Issue 4, November 2016

# Hardware Trojan Classification scheme Theory and Performance Analysis of Detection Techniques

#### Akanksha Dixit

Asst Professor, Dept of Electronics and Communication, Gyan Ganga College of Technology, RGPV, Jabalpur, India

Abstract: Devices produced for security sensitive fields like military, banking or government applications often make use of integrated circuits. In these areas reliability and trust are of special importance and thus an in-depth evaluation of manufactured devices with respect to security vulnerabilities is an essential task. Most of these institutions have departments that can take care of the chip-design but they rely on third party companies to actually produce the semiconductor chips in their factories. This is a very common scenario these days, where a trend towards separation of chip-design and fabrication is clearly observable. This is due to the high costs to build and maintain state- of-the-art semiconductor factories, which only pays off when the factories are used to capacity. With outsourced chip fabrication, are security sensitive chip designs still trustworthy? Every employee of the manufacturing chain from design to package assembly might maliciously modify the hardware! Therefore there is an urgent need to employ detection techniques for so called "Trojan hardware".

Keywords: Hardware Trojan; partial reconfiguration; hardware security; Trojan triggering.

#### I. INTRODUCTION

tasks is a common method to increase companies revenues. A company can only be competitive if their products are more advanced (i.e. higher complexity) or cheaper (due to cost pressure) than comparable products 3. Action phase (propagate payload) from its competitors. That is why Systems-On-Chip (SoA) or other embedded hardware devices are produced abroad. Physical Characteristics: From the perspective of a But, outsourcing poses a serious threat, especially for government agencies. Typically threatened sectors are the military, finance, power or the political sector. For example, critical applications are access control systems or ATMs that rely on embedded hardware.

Therefore, techniques to detect hardware Trojans are in focus of IT- Security research.. If a Trojan is activated the functionality can be changed, the device can be destroyed or disabled, it can leak confidential information or tear down the security and safety. Trojans are stealthy, that means the precondition for activation is a very rare event.

#### **II. CLASSIFICATION OF TROJANS**

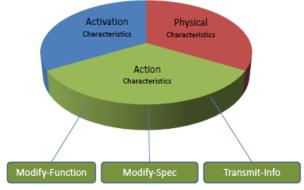

This section describes and illustrates what classes of In literature malicious Trojans exist. hardware implantations are called hardware Trojan horse (HTH), malicious circuit or malicious logic. A Trojan is completely characterized by its physical representation

Today's business is global and for this reason outsourcing and its behavior. So, its characterization can be divided into three parts:

- 1. Physical representation

- 2. Activation phase (trigger)

malicious circuit designer there are several physical characteristics to plan (figure 1). One of this physical Trojan characteristics is the type. The type of a Trojan can be either functional or parametric. A Trojan is functional if the adversary adds or deletes any transistors or gates to the original chip design. The other kind of Trojan, the parametric Trojan, modifies the original circuitry, e.g. thinning of wires, weakening of Flip-Flops or transistors, subjecting the chip to radiation, or using Focused Ion-Beams (FIB) to reduce the reliability of a chip.

Figure 1: Classification of Trojans: Physical Aspects

### International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

#### SITES

#### Smart And Innovative Technologies In Engineering And Sciences

Gyan Ganga College of Technology Vol. 4, Special Issue 4, November 2016

Then, this kind of Trojan is called "parametric Trojan". Action Characteristics: The effect of a Trojan can be seen designer has to define the size that is the next category.

The size of a Trojan is its physical extension or the the adversary (transmit key information). In [8] the authors number of components it is made of. Trojan can consist of only few components, so the area is small where the malicious logic occupies the layout of the chip. In contrast this is called tight distribution.

Activation Characteristics: Figure 2 illustrates the Trojans is that the chip consumes more power, so implicit activation characteristics. The typical Trojan is conditionbased: It is triggered by sensors, internal logic states, a measure the power consumption like 3.4.1, 3.4.2 or 3.4.3. particular input pattern or an internal counter value. Condition-based Trojans are detectable with power traces to some degree when inactive. That is due to the leakage destruction of the chip by extreme heat. The contrary term currents generated by the trigger or counter circuit of implicit Trojan is explicit Trojan. activating the Trojan. Hardware Trojans can be triggered in different ways. A Trojan can be internally-activated, that means it monitors one or more signals inside the IC. The malicious circuitry could wait for a countdown logic an attacker added to the chip, so that the Trojan awakes after a specific timespan.

Figure 2: Classification of Trojans: Activation

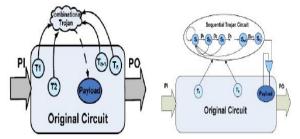

Figure 3: Illustration of a combinational and sequential Trojan (Source: [7])

The opposite is externally-activated. There can be malicious logic inside a chip that uses an antenna or other sensors the adversary can reach from outside the chip. For example a Trojan could be inside the control system of a cruising missile.

Furthermore, an malicious designer has to define the size from figure 4. It modifies the chip's function or changes that is the next category. Furthermore, an malicious the chip's parametric properties (e.g. provokes a process delay). Confidential information can also be transmitted to introduce the terms implicit Trojan and explicit Trojan. These terms are used to distinguish Trojans that induce small signal path delays or distinct signal path delays. The authors present a technique to measure signal path delays (see 3.4.4). Another important characteristic of these Trojans are well detectable by detection methods that The reason for this high power consumption can be, for example, the activation of a radio transmitter or the

Figure 4: Classification of Trojans: Action

#### **III. TECHNIQUES TO DETECT TROJANS**

In this section we will discuss several detection techniques in some detail. In general, there are some challenges a detection technique has to master. An advanced detection technique should deal with the typical variation in the manufacturing process

- handle large and complex micro architectures •

- detect small malicious Trojans

- detect any type of Trojans (classification)

- be non-destructive

- be scalable

- authenticate chips in a short time minimize the costs

#### **IV. FUNCTIONAL TESTING**

#### ATPG-based Trojan Detection

ATPG is acronym for automatic test pattern generation. This method is useful to detect parametric Trojans (malicious alterations that modify the circuitry): The netlist, i.e., the connectivity of an electronic design, is the

### International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

#### SITES

#### Smart And Innovative Technologies In Engineering And Sciences

Gyan Ganga College of Technology

Vol. 4, Special Issue 4, November 2016

same with and without the parametric Trojan. This IC Fingerprinting methodology detection method stimulates the input ports of a chip and This section deals with an effective, well-established monitors the output to detect manufacturing faults. If the detection methodology: power signals are used as a side logic values of the output do not match the genuine channel. The advantage of this method is, that this pattern, then a defect or a Trojan could be found. A test operation detects Trojans that cannot be detected by pattern (input vector) is a digital stimulus. This stimulus is applied to the input pins of the chip, then the digital output is inspected (digital measurement). Typically, a number of input patterns that cause faulty circuit behavior are used. This set of input vectors is derived from a fault model that is a mathematical description of the fault behavior of the circuitry. It can be infeasible, depending on the complexity of the chip and the pin layout, to search for the activation vector of a condition-based functional Trojan. The complexity of this search can be calculated with the common methods (combinatory) to estimate the effort to search a secret key.

#### **Built-In-Self-Test Techniques**

A Built-In-Self-Test (BIST) is an additional functionality of a chip. The chip consists of components that provide the key functionality of the device. Furthermore, the chip design defines additional circuitry to monitor signals or detect defects. On the one hand these techniques are used to detect manufacturing errors, but on the other hand a malicious logic could be detected via manufacturing tests. BIST functionality can be successful to detect malicious logic. In the following two sections two different BIST techniques are depicted, but there exist more concepts.

Three examples are: 1.Design for Debug: preferably used to detect manufacturing faults 2. Linear Feedback Shift Register Seeds: for more information. 3. The Design Tag System: advanced concept that is analog to DEFENSE logic

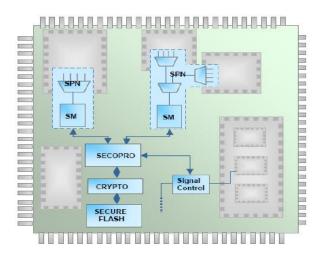

#### DEFENSE Logic

Another Built-In-Self-Test technique is called Design-For-Enabling-Security Chip with Additional DEFENSE Logic [13] logic (DEFENSE logic). The idea is to implement a robust inspection system in every chip analog to the immune systems in biological organisms This security logic consists of sensors, a central control unit and a signal method describes how a genuine fingerprint is generated control unit. This concept seems very expensive and from a set of values. A power trace is a discrete-time complex. The design of the chip Contra takes more time signal that consists of continuous values of power because of the additional DEFENSE logic. The insertion consumption. The power trace r(t; I;C;M) is of the DEFENSE logic is done at the design phase (at RTL measured, while the chip I is processing the calculation C (Register Transfer Language)), that the advisory is able to under influence of the power measurement M. This is the analyze the security system in detail. But there are some power trace of a genuine IC: advantages: This built-in system is useful to monitor Pro  $r_G(t; I;C;M) = p(t;C) + n_p(t;I;C) + n_m(t;M)$ the functional logic in use (on-line monitoring). It is and this equation defines the power trace of a Trojan IC: reconfigurable because of the Security and Control  $r_T(t; I;C;M) = p(t;C) + n_p(t; I;C) + n_m(t;M) + \tau(t; I;C)$ Processor and the ash memory. Furthermore, it is non- I destructive. Multiple and different sensors could detect C functional or parametric Trojans simultaneously.

functional analysis. This is a rough Sequence overview:

1. Generate genuine fingerprints from intensely tested chips, that is

(a) Select a few ICs out of one family of chips at random (b) Analyze their functionality (e.g. stimulate I/O ports with input and measure the output)

(c) Measure and analyze their side channel signal

(d) Use destructive reverse engineering (see 3.1) to validate the originality of the ICs (in this step, the chips will be destroyed)

(e) Create (i.e. calculate) the fingerprint from the measured values

2. Authenticate the other chips of this family by comparing the genuine fingerprint and the measured fingerprint.

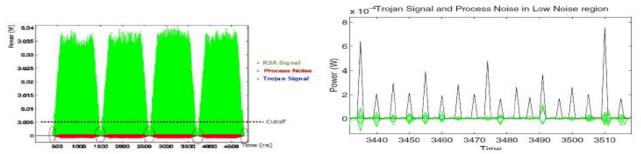

Trojan Detection with Power Traces Fingerprints are deduced from functional tests or side channels, but how is a Trojan detected in the measured values? The following

Integrated Circuit I

actual Calculation on I during the measurement (typically, the same calculation during the analysis)

### International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

#### SITES

Gyan Ganga College of Technology

Vol. 4, Special Issue 4, November 2016

Μ Power measurement on I t Time points (discrete-time time-stamps) r(t; I;C;M) Power trace p(t;C) Mean power consumption

$n_p(t; I;C)$  Process noise n<sub>m</sub>(t;M) Measurement noise  $\tau$ (t; I;C) Extra power leakage

Figure 7: Left Figure: Illustration of low Process Regions, Right Figure: Process Noise Signal and Trojan IC Signal [10]

| Detection    | resolution  | Trojan     | Comple | Destruc | Scal-   | Costs | phase of IC | Features               |

|--------------|-------------|------------|--------|---------|---------|-------|-------------|------------------------|

| Technique    |             | Types      | -xity  | -tive   | ability |       | life cycle  |                        |

| ATPG-        | unknown     | parametric | mid    | no      | high    | low   | test-time   |                        |

| based        |             | Trojans    |        |         |         |       |             |                        |

| Trojan       |             |            |        |         |         |       |             |                        |

| Detection    |             |            |        |         |         |       |             |                        |

| DEFENSE      | sensor      | functional | high   | no      | high    | high  | run-time    | reconfigurable         |

| logic        | dependent   | Trojans    | -      |         | -       |       |             | multiple sensors,      |

|              |             |            |        |         |         |       |             | signal control<br>unit |

| IC           | Down to     | functional | mid    | no,     | mid     | mid   | Test-time   |                        |

| Fingerprinti | 0.1% -      | Trojans,   |        | except  |         |       |             |                        |

| ng           | 0.01% of    | parametric |        | few     |         |       |             |                        |

| 0            | total       | Trojans    |        | IC's    |         |       |             |                        |

|              | circuitry   | J          |        |         |         |       |             |                        |

| Region-      | Down to     | functional | mid    | no,     | mid     | mid   | Test-time   | localisation           |

| based        | 1% of total | Trojans    |        | except  |         |       |             |                        |

| Partitioning | gate count  | U U        |        | few     |         |       |             |                        |

| U            | C           |            |        | IC's    |         |       |             |                        |

| Path Delay   | Down to     | functional | mid    | no,     | mid     | mid   | Test-time   |                        |

| Fingerprinti | about1% of  | Trojans,   |        | except  |         |       |             |                        |

| ng           | the chip    | parametric |        | few     |         |       |             |                        |

|              | _           | Trojans    |        | IC's    |         |       |             |                        |

Table 1: Table of Characteristics of the Detection Methods.

Advanced Detection with Reduced Frequency The C; VDD and Qse technology dependent parameters detection results can be better if the frequency of the tested f Clock frequency chip is reduced. Hence, the frequency must have an N Switching activity influence to the measured values. One common side Ileak Leakage current channel is the power consumption of an IC. The total power consumption P of a chip is:

$$P = \left(\frac{1}{2} . C. Vdd^{2} + Qse. Vdd\right). f. N + Ileak. Vdd$$

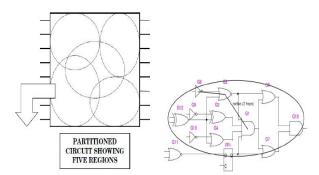

Region-based Partition and Excitation Technique This approach is clearly represented in [2]. The method stimulates specific parts of the integrated circuitry to analyze the power consumption more precise. This

### International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

#### SITES

#### Smart And Innovative Technologies In Engineering And Sciences

Gyan Ganga College of Technology

Vol. 4, Special Issue 4, November 2016

defects of sequential circuits [6]. In the context of this chip to analyse the timing behavior. technique a region is an important term. It is a connected set of gates. The goal is to "cluster the flip-flops into groups that are most likely to be associated with a Trojan" [2]. This detection method uses the power consumption P of the chip as the side channel. Because the power consumption depends on frequency, the chip is clocked at low operating frequency during this analysis. The power consumption P is simplified compared to the definition in 3.4.1, because the accuracy is sufficient in this case.

$$P = C. Vdd^2.f$$

C, Vdd Technology dependent parameters

f Clock frequency

The Power Profile is a set of values .Each value represents the vector. The measured value of the power consumption is an indicator for the switching activity in a particular region of the chip.

Every detection method consists of several steps. The region-based partition and executes as follows: Sequence

- 1. select regions for analysis

- 2. generate input vectors

- 3. measure the power profile

- Path Delay Fingerprinting

Often, the side channel signal power consumption can be too vague. In this section, a more elaborate detection technique is explained. The paper [8] describes a method patterns or activation vectors. Several techniques exist, but to analyze the netlist of a chip, whereas [16] depicts a some are just concepts or simulations, so tests with real more practical method to measure path delays in fabricated ICs should be conducted. integrated circuits.

Figure 10: Illustration of the Term Regions and one Region with Radius 2[2]

The measurement of timing information seems to be slightly better than the measurement of power consumption. On the one hand a path delay fingerprint of an IC can be the set of path delay values that are measured on the pins of the chip. But, another method uses timing information measured between two registers (register-toregister path delay) to detect malicious alterations. The

technique was first used for detection of manufacturing former and more theoretical method uses the netlist of the

#### **V. CONCLUSION**

The analysis of ICs is expensive and there can be adversaries that apply to all Alternatives characteristics of the attacker. But then the potential of threat can be lower. In this case other techniques can be used. Obfuscation and camouflage can be useful to reduce the furor. These techniques hide the interesting chip to some extend. Further investigations should include detection methods that detect ad- Perspective aditional or malicious electronic devices like additional ICs or transistors on a complex printed circuit board (PCB). An additional wire on a PCB that bypasses an encryption chip when a particular condition occurs also is a hardware Trojan that is easy to hide. New experiments that comply with doubleblind and randomized test operations could prove the practical benefit of the detection techniques.In this paper the reader was introduced to a classification scheme Theory and many terms concerning Trojan detection. The most detection methods use one side channel signal to find malicious circuitry. Some problems remain even if successful detection techniques exist. A practical detection method should be low-cost, scalable, fast-detecting and Praxis effective. In general it is more difficult to find unknown/malicious circuits than to check for known

#### REFERENCES

- [1] Mainak Banga and Michael S. Hsiao: A Region Based Approach for the Identification of Hardware Trojans, Bradley Department of Electrical and Computer Engineering, Virginia Tech., Host'08, 2008.

- A. L. DSouza and M. Hsiao: Error diagnosis of sequential circuits [2] using region-based model, Proceedings of the IEEE VLSI Design Conference, January, 2001, pp. 103-108.

- C. Fagot, O. Gascuel, P. Girard and C. Landrault: On Calculating [3] Eficient LFSR Seeds for Built-In Self Test, Proc. Of European Test Workshop, 1999, pp 7-14.

- [4] Rajat Subhra Chakraborty, Somnath Paul and Swarup Bhunia: On-Demand Transparency for Improving Hardware Trojan Detectability, Department of Electrical Engineering and Computer Science, CaseWestern Reserve University, Cleveland, OH, USA

- Yier Jin and Yiorgos Makris: Hardware Trojan Detection Using [5] Path Delay Fingerprint, Department of Electrical Engineering Yale University, New Haven

- Reza Rad, Mohammad Tehranipoor and Jim Plusquellic: Sensitivity [6] Analysis to Hardware Trojans using Power Supply Transient Signals, 1st IEEE International Workshop on Hardware-Oriented Security and Trust (HOST'08), 2008.

- Dakshi Agrawal, Selcuk Baktir, Deniz Karakoyunlu, Pankaj [7] Rohatgi and Berk Sunar: Trojan Detection using IC Fingerprinting, IBM T.J. Watson Research Center, Yorktown Heights, Electrical & Computer Engineering Worcester Polytechnic Institute, Worcester, Massachusetts, Nov 10, 2006

### International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

#### SITES

#### Smart And Innovative Technologies In Engineering And Sciences

Gyan Ganga College of Technology

Vol. 4, Special Issue 4, November 2016

- [8] Xiaoxiao Wang, Mohammad Tehranipoor and Jim Plusquellic: Detecting Malicious Inclusions in Secure Hardware, Challenges and Solutions, 1st IEEE International Workshop on Hardware-Oriented Security and Trust (HOST'08), 2008

- [9] Miron Abramovici and Paul Bradley: Integrated Circuit Security -New Threats and Solutions

- [10] Tom Kean, David McLaren and Carol Marsh: Verifying the Authenticity of Chip Designs with the DesignTag System

- [11] S. Mitra, and K.S. Kim: X-Compact An Eficient Response Compaction Technique, IEEE Tran. on CAD, vol. 23, no. 3, pp. 421432, Mar. 2004.

- [12] Jie Li and John Lach: At-Speed Delay Characterization for IC Authentication and Trojan Horse Detection, 1st IEEE International Workshop on Hardware-Oriented Security and Trust (HOST'08), 2008

- [13] Sun Tzu: The Art of War, 6th century BC, China

- [14] J. M. Soden, R. E. Anderson, C. L. Henderson: IC Failure Analysis: Magic, Mystery, and Science. In: IEEE Design & Test of Computers, Vol. 14, pp. 5969, 1997.

- [15] M. Tehranipoor, H. Salmani, X. Zhang, X. Wang, R. Karri, J. Rajendran, K. Rosenfeld, —Trustworthy hardware: Trojan detection and design-for-trust challenges, Computer (2011)

- [16] M. Tarek Ibn Ziad, A. Al-Anwar, Y. Alkabani, M. W. El-Kharashi, H. Bedour, -E-voting attacks and countermeasures, In Proceedings of the 10th International Symposium on Frontiers of Information Systems and Network Aplications (FINA 2014), held in conjunction with the 28th IEEE International Conference on Advanced Information Networking and Applications (AINA-2014), Victoria, BC, Canada, 2014, pp. 269-274.

- [17] OpenCores. Online: http://opencores.org/ (accessed April 2016)